FPGA là viết tắt của thuật ngữ tiếng anh “Field programmable Gate Array”, nghĩa là Mảng cổng lập trình được dạng trường. FPGA thuộc họ ASIC lập trình được

* Ý nghĩa và vai trò của FPGA

ASIC lập trình được đã xuất hiện từ lâu dưới dạng PLD (Programmable Logic Device), nhưng vai trò của các dạng ASIC này là không nhiều vì số lượng cổng trên Chip rất ít dẫn tới chức năng của các PLD này cũng nghèo nàn và thường chỉ sử dụng với những nhiệm vụ rất hạn chế trong toàn hệ thống. Kể từ năm 1980,Các công ty sản xuất PLD hàng đầu đã đẩy mạnh quá trình nghiên cứu về FPGA và nhanh chóng cho ra các thế hệ FPGA với số lượng cổng và tốc độ ngày càng cao.các FPGA hiện nay có số lượng cổng đủ lớn để có thể thay thế cả một hệ thống bao gồm lõi CPU, Bộ điều khiển bộ nhớ (Memory Controller), các ngoại vi như SPI,Timer, I2C, GPIO, PWM, Video/Audio Controller… (nghĩa là tương đương với các SoC hiện đại).Tuy nhiên,FPGA không thể nào so sánh được với ASIC và SoC cả về kinh tế lẫn tốc độ hoạt động. Nhưng bù lại, với khả năng tái cấu hình mạnh, FPGA đóng một vai trò vô cùng to lớn trong việc giảm giá thành và thời gian chế tạo ASIC bằng cách sử dụng FPGA trong quá trình thiết kế luận lý trước khi đưa ra sản xuất các ASIC mẫu. Quy trình sản xuất Chip ASIC bằng cách này gọi là fabless rất phổ biến hiện nay trên thế giới, giúp các công ty nhỏ và vừa và đặc biệt là các nước yếu về công nghệ như Việt nam tham gia vào thế giới của IC.

Để giải thích cho các bạn hiểu rõ hơn sự quan trọng rất lớn của FPGA, tôi sẽ cho các bạn một ví dụ rõ hơn. Trước đây, khi muốn chế tạo ra 1 con Chip Vi Xử Lý.Người ta phải thiết kế Chip ở mức logic sử dụng các ngôn ngữ mô tả phần cứng, Để kiểm tra công đoạn này người ta sử dụng những phần mềm mô phỏng.Sau đó thiết kế phải được tổng hợp dựa trên các thư viện cấp thấp của hãng mà bạn sẽ sản xuất của con Chip của bạn sau này, sau đó là quá trình kiểm tra timing (định thời) cho toàn bộ thiết kế để đảm bảo thiết kế của bạn sẽ hoạt động ở tần số yêu cầu.Tất cả các công đoạn này đều chỉ có thể kiểm tra bằng các phần mềm mô phỏng (Điều này dẫn tới nguy cơ xảy ra sai xót rất lớn khi chuyển thiết kế sang môi trường Chip thực ). Sau đó bạn sẽ gởi thiết kế của mình tới công ty sản xuất Chip và phó mặc cho số phận,một chip mẫu giá vài triệu đô la sẽ được chuyển cho bạn, và sau đó bạn bắt đầu quá trình test chip trong môi trường thực, nếu thất bại, khả năng lớn là bạn sẽ phải thực hiện lại hoàn toàn qui trình thiết kế như đã nói ở trên, và cứ mỗi lần như vậy, bản sẽ phải bỏ sọt rác nhiều triệu đô la và khỏag thời gian nghiên cứu rất lớn, quy trình này làm cho các đất nước nghèo như việt nam không thể tham gia vào các cuộc chơi của các đất nước giàu có trong thế giới của ASIC. Nhưng với FPGA,bạn không những có thể rút ngắn thới gian thực hiện ASIC mà còn giảm chi phí nghiên cứu tối đa do quá trình kiểm tra thiết kế không những được kiểm tra bằng các phần mềm mô phỏng mà giờ đây còn có thể chạy trên các Chip thực trong mội trường có thể nói là gần với môi trường ASIC thực nhất. Khả năng tái cấu hình cho phép bạn sửa đi sửa lại thiết kế cho đến khi đạt yêu cầu mà không tốn một xu nào ngoài tiền điện mà bạn phải trả.

* Một ứng dụng quan trọng và thiết thực hơn đối với chúng ta (tôi và các bạn)

Có lẽ đọc phần trên chúng ta có thể hình dung ra ý nghĩa to lớn, vai trò quan trọng của FPGA. Nhưng sản xuất ASIC vẫn là một điều quá xa vời đối với đại đa số chúng ta, có ai trong số các bạn tự hỏi tại sao không sử dụng trực tiếp FPGA như là một sản phẩm cuối cùng của bạn, có ai cấm hay thu tiền bản quyền của chúng ta về việc đó đâu. Thực tế là FPGA rất hay được sử dụng trong các hệ thống SDR (Software Defined Radio) vì khả năng tái cấu hình giúp các chức năng của thiết bị có thể thay đổi nhanh chóng, bạn có thể hỏi rằng một hệ thống CPU/MCU/DSP cũng có thể làm được chuyện này dễ dàng? Nhưng thực ra thì có nhiều những ứng dụng tốc độ cao mà các MCU thậm chí cả các CPU/DSP trung bình cũng phải bất lực.

* Tại sao phải dùng FPGA trong khi bạn đó nắm trong tay MCU/CPU thậm chí cả các DSP cực mạnh

+ MCU/CPU/DSP vẫn cần các hardware khác bên cạnh trong các ứng dụng chuyên dụng

+ Để điều khiển VGA sử dụng CPU làm controller cần CPU với tốc độ 27Mhz hoạt động 100% CPU

+ Các ứng dụng xử lý hình ảnh/video, các ứng dụng mạng neuron,IA cần tốc độ xử lý rất lớn. Mặc dù các DSP đủ mạnh và các SoC mạnh có thể thực hiện được, nhưng sự lựa chọn còn phụ thuộc vào vấn đề kinh tế

+ Có bao giờ bạn nghĩ mình sẽ thiết kế ra 1 con CPU của chính mình, với FPGA bạn hoàn toàn có thể thực hiện điều đó

+ Đến với FPGA,bạn có cơ hội để tiếp cận gần nhất thế giới của IC

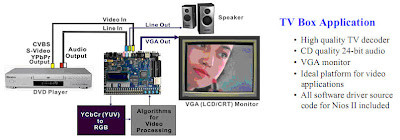

+ Bạn có thể thực hiện một hệ thống với đầy đủ CPU/Peripheral/IO… và kết nối chúng theo ý muốn,hoặc thậm chí một hệ thống đầy đủ không cần cả CPU như các Chip giải mã/nén Video/Audio, các Chip xử lý hình ảnh/giọng nói, các Chip PID Motor Controller, networking chip …

* Kit phát triển FPGA và các ứng dụng demo :

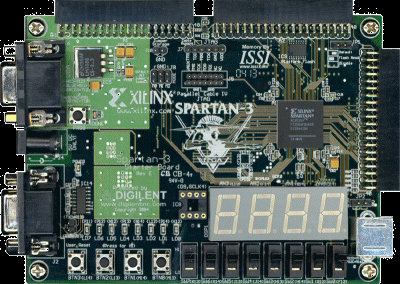

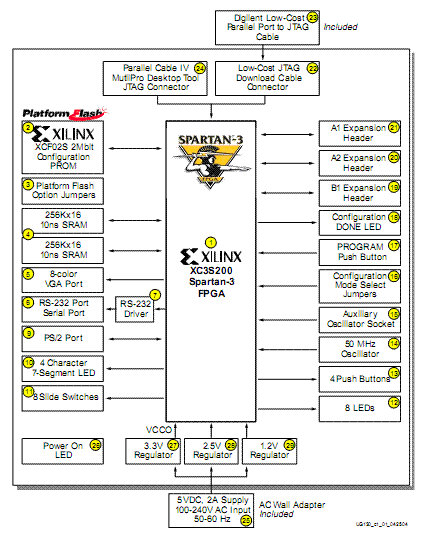

Kit Xilinx Spartan-3 FPGA Starter Kit Board (Giá $149.00)

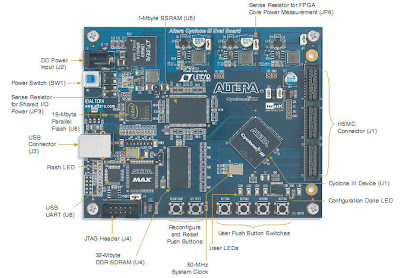

Kit Altera Cyclone III FPGA Starter Kit (Giá $199.00)

Kit Altera Cyclone III FPGA Starter Kit (Giá $199.00)

Các Kit trên là Starter Kit, nhìn nhiều Chip vậy thôi chứ thực ra chỉ có mỗi con FPGA là chính thôi,mấy con còn lai chủ yếu là SRAM/DRAM, Flash, Bộ config Nguồn và các ngoại vi…

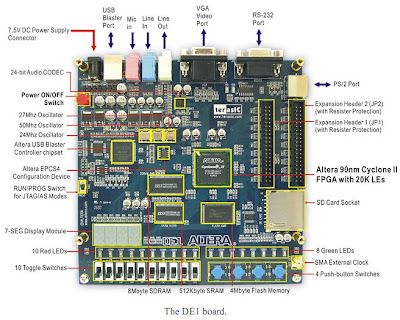

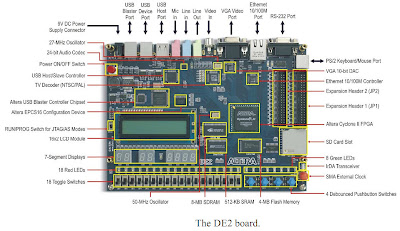

Dưới đây là các Kit giáo dục rất mạnh của Altera (DE1,DE2) đã được dùng phổ biến ở nhiều trường đại học trên thế giới (Kit do Terasic thiết kế chế tạo).Nếu ai đang là sinh viên điện tử năm 3,4 ở các trường ĐH BK TPHCM và ĐH Tự Nhiên TPHCM thì có lẽ biết rõ về loại Kit này.

Altera DE1 - Development and Education Board (Giá $150.00)

Altera DE2 - Development and Education Board (Academic price :$269)

Các Kít phát triển FPGA thì đa dạng và dùng cho nhiều mục đích khác nhau nhưng đều gồm 5 phần chính : FPGA, Bộ nhớ (SRAM/DRAM/Flash), Ngoại vi, bộ cấu hình (Configuration device), và bộ nguồn.

Nhìn hai loại board ở trên, 1 cái thì mạch diện,IC dày đặc,1 cái thì nhìn đơn giản, nhưng thực thế chỉ là các Kit DE có các ngoại vi đi kèm để dùng cho các mục đích phát triển khác nhau, còn con chip FPGA thì cũng tương đượng thôi, thâm chí còn yếu hơn các Starter Kit.

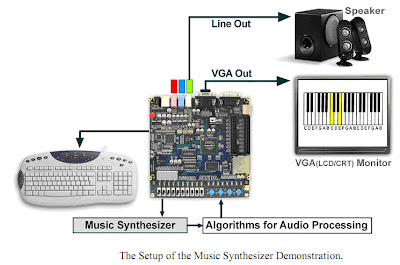

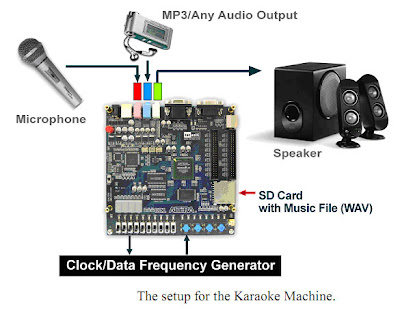

Các ứng dụng demo của Kit phát triển Altera DE1,DE2